### (19) United States

## (12) Patent Application Publication (10) Pub. No.: US 2007/0063935 A1

Mar. 22, 2007 (43) **Pub. Date:**

#### (54) DISPLAY DEVICE AND DRIVING METHOD **THEREOF**

#### (75) Inventor: Yasunori YOSHIDA, Atsugi (JP)

Correspondence Address: FISH & RICHARDSON P.C. P.O. BOX 1022 **MINNEAPOLIS, MN 55440-1022 (US)**

(73) Assignee: **SEMICONDUCTOR ENERGY** LABORATORY CO., LTD., Atsugi-shi

(21) Appl. No.: 11/530,771

(22)Filed: Sep. 11, 2006

(30)Foreign Application Priority Data

Sep. 15, 2005 (JP) ...... 2005-269013

#### **Publication Classification**

(51) Int. Cl. G09G 3/30 (2006.01)

#### (57)**ABSTRACT**

To solve the lack of program time, which is a problem of a display device including an EL element, and to provide a display device including a pixel circuit with a high aperture ratio and a driving method thereof. In a circuit including a driving transistor, a capacitor, a display element which can be used as a capacitor, a first power supply line and a second power supply line, potentials of the first power supply line and the second power supply line are set to be almost the same, thereby a threshold voltage of the driving transistor is held in the display element, and after that, a charge is divided into the display element and the capacitor.

# FIG. 1

FIG. 3

FIG. 4A

FIG. 6

FIG. 7

FIG. 8

FIG. 9

FIG. 12A

FIG. 12B

FIG. 13B

## DISPLAY DEVICE AND DRIVING METHOD THEREOF

#### TECHNICAL FIELD

[0001] The present invention relates to a display device to which a self-light emitting type display element is applied and a driving method thereof.

#### BACKGROUND ART

[0002] In a driving method of a display device, there are an active matrix drive and a passive matrix drive mainly. A passive matrix drive has a structure that a display element is sandwiched between electrodes arranged in matrix, which can be manufactured at low cost. However, when one pixel is driven, other pixels cannot be driven so that it is not good for a large-area or high-definition display device. On the other hand, an active matrix drive has an active element and a unit for holding luminance data in each pixel, so that manufacturing cost is higher than a passive matrix drive. However, while one pixel is driven, other pixels can emit light holding luminance data. Therefore, an active matrix driving method is used for most of large-area or high-definition display devices.

[0003] An active matrix display device has a unit for holding luminance data in each pixel as described above. The display device can be classified by whether the luminance data has a digital value or an analog value. When the luminance data has a digital value, a light emitting element has only a binary value of on or off, thereby a display image has only two gray scales. A method of expressing multi gray scale by displaying images of binary values quickly and repeatedly is widely used (time gray scale method). In addition, when the luminance data has an analog value, luminance of a display element can be controlled with an intermediate value; therefore, a time gray scale method is not always required in order to express a multi gray scale.

[0004] An active matrix drive display device with luminance data having an analog value is mainly, for example, a liquid crystal display. A liquid crystal display has been spread widely, but has problems such as unfitness for displaying a moving image because of slow response speed, and dependence on viewing angle. In addition, a display element is not self-light emitting type; therefore, a back light is required so that power consumption is high. Therefore, development of a new display device replacing a liquid crystal display is expected.

[0005] On the other hand, a display device of so-called self-light emitting type, of which a pixel is formed of a light emitting element such as a light emitting diode (LED) attracts attention. As a light emitting element employed for a self-light emitting type display device, an organic light emitting diode (also called OLED (Organic Light Emitting Diode), organic EL element, electroluminescence (EL) element, and the like) attracts attention and is becoming to be used for an EL display and the like. Because a light emitting element such as an OLED is self-light emitting type, a pixel has higher visibility, a back light is not required, and response speed is faster as compared to a liquid crystal display. Therefore, an active matrix drive display device which employs the organic EL element as a display element has been developed actively.

[0006] Here, a description is made of an organic EL element. Luminance of an organic EL element is determined by a flowing current value. This nature mainly causes a problem of an organic EL element driven by an active matrix drive. In other words, when a voltage of an analog value is written to a luminance data holding unit (e.g., a capacitor) of a pixel like a liquid crystal display, an active element controlling a current flowing to a display element is controlled in an analog manner, unlike a liquid crystal display in which a voltage applied to a display element is controlled in an analog manner. The active element is provided in each EL element; therefore, a variation in electrical characteristics of an active element in each pixel directly causes a variation in luminance.

[0007] Accordingly, when a current drive type display element such as an organic EL element is driven by an active matrix drive by an analog value, it is important to compensate a characteristic variation of an active element which drives a display element. For the method thereof for example, a current input type display element is employed in which a structure of a pixel circuit is devised.

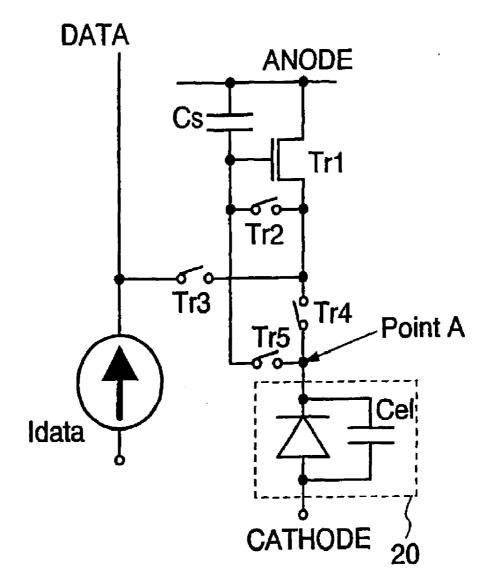

[0008] In a current input type pixel circuit, an analog current is employed as luminance data inputted to a pixel. Note that an analog current here refers a current outputted from a circuit which can control a current value by multilevel. An analog current (also referred to as a data current) made by such a peripheral driver circuit corresponding to luminance of a display element is supplied to an active element of each pixel, and a voltage applied to the active element at that time is held. As a result, the current value is held and may keep to be supplied to a display element even after a supply of data current is stopped. FIG. 8 shows an example of such a pixel circuit. A circuit shown in FIG. 8 includes a first power supply line ANODE, a second power supply line CATHODE, a current source for supplying a data current Idata, a wire DATA which the data current Idata flows, a display element 10, a driving transistor Tr1, a capacitor Cs as a luminance data holding unit, a switch Tr2 for connecting and disconnecting between a gate electrode and a drain electrode of the driving transistor Tr1, a switch Tr3 for selecting a pixel in which the Idata is supplied to the driving transistor Tr1, and a switch Tr4 for connecting and disconnecting between the display element 10 and the drain electrode of the driving transistor Tr1.

[0009] The current input type pixel circuit can keep supplying a data current as it is regardless of a characteristic of an active element, thereby being suitable for driving a current drive type display element by an active matrix drive. However, when a current value of a display element is very small when driven display element such as an organic EL element, there is a problem in that time (also referred to as program time) for charging the capacitor Cs becomes very long since a data current corresponds one-to-one to a current value of the display element 10 when driven in the circuit shown in FIG. 8.

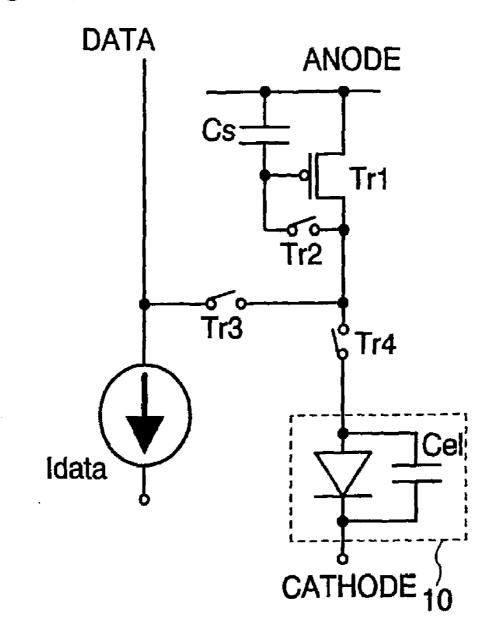

[0010] Therefore, a current input type pixel circuit is suggested in which a data current can be increased against a current value when a display element is driven by adding a capacitor in a pixel circuit (refer to Patent Document 1).

[Patent Document 1]

[0011] Japanese Patent Laid-Open No. 2004-310006

#### DISCLOSURE OF INVENTION

[0012] As an example of a conventional pixel circuit, a pixel circuit corresponding to FIG. 5 of Patent Document 1 is shown in FIG. 9 (Note that reference numerals are changed from those in Patent Document 1). A circuit structure of FIG. 9 corresponds to a pixel circuit where a capacitor Ct for holding a threshold value and a switch Tr6 for connecting a capacitor, which are connected in series, are added to the pixel circuit in FIG. 8.

[0013] In Patent Document 1, a threshold voltage of a driving transistor Tr1 is held in a capacitor Ct for holding a threshold value before a data current corresponding voltage (also referred to as Vgs (data)) is held in a capacitor Cs for holding a threshold value, and Ct and Cs are connected after holding Vgs (data) in Cs, thereby a data current may be larger than a current value when a display element is driven. In addition, the difference thereof becomes larger as a capacitance value of Ct in response to a capacitance value of Cs is larger. A program time may be shortened by increasing a data current. Note that, a relationship of a current value (Ioled) when a display element is driven and a data current (Idata) is shown in equation 1.

$$loled = \left(\frac{Cs}{(Ct + Cs)}\right)^2 \times Idata$$

[Formula 1]

[0014] Time to write a data current to one pixel is a value obtained by dividing one flame period (about one-60th second) by the number of scan lines, and the time for a display device with 320 scan lines is about 50 μ second. On the other hand, it takes several ms to charge parasitic capacitance of a data line enough when a display element (e.g. an EL element) has a drive current of about several tens nA and a data current is also about several tens nA. Charging time is proportional to a current value; therefore, by calculations, a data current need to be about a hundred times as large as a current value supplied to a display element in order to write a data current to a pixel within several tens µ seconds. That is, in the case where a data current is written in the way described in Patent Document 1, a capacitance value of a threshold holding capacitor Ct is required to be about ten times as large as that of a Vgs (data) holding capacitor Cs. Cs is required to have a certain amount of capacitance in order to hold Vgs (data); therefore, an area of Ct is required to be larger to increase a data current.

[0015] However, the proportion of the area of Ct to an area of a pixel becomes larger as the area of Ct becomes larger, and an area (referred to as aperture ratio) where a light emitting area of a display element occupies in the pixel area is decreased. If Ct is required to be about ten times as large as Cs, a decrease in aperture ratio is a serious problem. Luminance becomes lower because of a decrease in aperture ratio even if the same voltage and a current with the same current density as when the aperture ratio is high, are supplied to a display element. To get the same luminance, a higher voltage is required to be applied to a display element so that a current with a higher current density is supplied to a display element, which causes higher power consumption. In addition, there is a problem in reliability and lifetime of a display element when a current with a higher current density is supplied to a display element.

[0016] As described above, when program time is shortened to be within normal program time by using the pixel structure of Patent Document 1, Ct is required to be larger; therefore, a decrease in aperture ratio of a pixel is occurred. A decrease in aperture ration causes a problem such as luminance, power consumption, reliability, and lifetime.

[0017] In view of the foregoing problems, the present invention provides a current input type pixel circuit, which has shorter program time and high aperture ratio of a pixel.

[0018] In view of the forgoing subject in the invention, a display element functions as a capacitor. A threshold voltage of a transistor, which drives a display element, can be written to the capacitor. Therefore, the threshold voltage of a transistor can be written without providing a capacitor for holding a threshold value.

[0019] Hereinafter, description is made of a specific structure of the invention.

[0020] One mode of the invention is a display device including a plurality of data lines for supplying a data current, a plurality of scan lines for transmitting a selection signal, a pixel portion including a plurality of pixel circuits which are connected to data lines and scan lines. Each pixel circuit includes a display element which emits light with luminance corresponding to a data current, a first transistor which supplies a data current to the display element and has a source electrode, a drain electrode, and a gate electrode, a first power supply line on a high potential side, which is the same potential as an anode of the display element, a second power supply line on a low potential side, which is the same potential as a cathode of the display element, a first capacitor for holding a voltage between the source electrode and the gate electrode of the first transistor, a second transistor for selecting a connection between the drain electrode and the gate electrode of the first transistor, a third transistor for selecting a pixel circuit to which a data current is written by selecting a connection between the data line and the pixel circuit, a fourth transistor for selecting a connection between the first transistor and the display element, and a fifth transistor selecting a connection between the capacitor and the display element. The display element functions as a second capacitor.

[0021] Another mode of the invention is a display device including a plurality of data lines for supplying a data current, a plurality of scan lines for transmitting a selection signal, a pixel portion including a plurality of pixel circuits which are connected to data lines and scan lines. Each pixel circuit includes a display element which emits light with luminance corresponding to a data current, a first transistor which supplies a data current to the display element and has a source electrode, a drain electrode, and gate electrode, a first power supply line and a second power supply line, in either of which a potential changes, a first capacitor for holding a voltage between the source electrode and the gate electrode of the first transistor, a second transistor for selecting a connection between the drain electrode and the gate electrode of the first transistor, a third transistor for selecting a pixel circuit to which a data current is written by selecting a connection between the data line and the pixel circuit, a fourth transistor for selecting a connection between the first transistor and the display element, and a fifth transistor for selecting a connection between the first capacitor and the display element. The display element functions as a second capacitor.

[0022] Another mode of the invention is a display device including a data line driver circuit, a plurality of data lines connected to the data line driver circuit, a scan line driver circuit, a plurality of scan lines connected to the scan line driver circuit, a pixel portion including a plurality of pixel circuits connected to the data lines and the scan lines. Each pixel circuit includes a display element which emits light with luminance corresponding to a data current which is supplied from the data lines, a first transistor which supplies the data current to the display element and has a source electrode, a drain electrode, and a gate electrode, a first power supply line and a second power supply line, in either of which a potential changes, a first capacitor for holding a voltage between the source electrode and the gate electrode of the first transistor, a second transistor which is controlled by the scan line driver circuit and selects a connection between the drain electrode and the gate electrode of the first transistor, a third transistor for selecting a pixel circuit to which the data current is written by selecting a connection between the data line and the pixel circuit, a fourth transistor for selecting a connection between the first transistor and the display element, and a fifth transistor for selecting a connection between the first capacitor and the display element. The display element functions as a second capacitor.

[0023] Another mode of the invention is a driving method of a display device including a first transistor, a second transistor connected to the first transistor, a third transistor provided between the first transistor and a current source, a display element, a fourth transistor and a fifth transistor which are provided between the display element and the first transistor. A light emitting period for which the display element is emitted after a threshold writing period for storing a charge in the display element is provided within one frame period. In the threshold writing period, the first transistor is turned on, the second transistor is turned on, the third transistor is turned off, the fourth transistor is turned off, and the fifth transistor is turned on. In the light emitting period, the second transistor is turned off, the third transistor is turned off, the fourth transistor is turned on, and the fifth transistor is turned off.

[0024] Another mode of the invention is a driving method of a display device including a first transistor, a second transistor connected to the first transistor, a capacitor connected to the first transistor and a power supply line, a third transistor provided between the first transistor and a current source, a display element, a fourth transistor and a fifth transistor which are provided between the display element and the first transistor. A light emitting period for which the display element is emitted is provided after a Cs rewriting period for dividing a charge into the display element and the capacitor within one frame period. In the Cs rewriting period, the second transistor is turned off, the third transistor is turned off, the fourth transistor is turned off, and the fifth transistor is turned on. In the light emitting period, the second transistor is turned off, the third transistor is turned off, the fourth transistor is turned on, and the fifth transistor is turned off.

[0025] Another mode of the invention is a driving method of a display device including a first transistor, a second transistor connected to the first transistor, a third transistor provided between the first transistor and a current source, a display element, a fourth transistor and a fifth transistor which are provided between the display element and the first

transistor. A light emitting period for which the display element is emitted is provided after a threshold writing period for storing a charge in the display element within one frame period. In the threshold writing period, the first transistor is turned on, the second transistor is turned on, the third transistor is turned off, the fourth transistor is turned off, and the fifth transistor is turned on, and a potential of a power supply line on a cathode side of the display element is the same or almost the same as a potential of a power supply line on an anode side of the display element. In the light emitting period, the first transistor is turned on, the second transistor is turned off, the third transistor is turned off, the fourth transistor is turned on, and the fifth transistor is turned off, and a potential of a power supply line on a cathode side of the display element is lower than a potential of a power supply line on an anode side of the display element.

[0026] Another mode of the invention is a driving method of a display device including a first transistor, a second transistor connected to the first transistor, a capacitor connected to the first transistor and a power supply line, a third transistor provided between the first transistor and a current source, a display element, a fourth transistor and a fifth transistor which are provided between the display element and the first transistor. A light emitting period for which the display element is emitted is provided after a Cs rewriting period for dividing a charge into the display element and the capacitor within one frame period. In the Cs rewriting period, the second transistor is turned off, the third transistor is turned off, the fourth transistor is turned off, and the fifth transistor is turned on, and a potential of a power supply line on a cathode side of the display element is the same or almost the same as a potential of a power supply line on an anode side of the display element. In the light emitting period which comes after the Cs rewriting period, the second transistor is turned off, the third transistor is turned off, the fourth transistor is turned on, and the fifth transistor is turned off, and a potential of a power supply line on a cathode side of the display element is lower than a potential of a power supply line on an anode side of the display element.

[0027] In the invention, a driving method of a display device includes first to fifth transistors having the same polarity.

[0028] In the invention, a first transistor is a p-channel transistor, and one of a source electrode and drain electrode of the first transistor, which has a higher potential when a display element emits light, may be connected to a first power supply line.

[0029] In the invention, a first transistor is an n-channel transistor, and one of a source electrode and drain electrode of the first transistor, which has a lower potential when a display element emits light, may be connected to a first power supply line.

[0030] Another mode of the invention is a display device including first, second and third wires, a first capacitor, a display element, and first to fifth transistors. A gate electrode of the first transistor is connected to the first wire through the first capacitor. A first terminal of the first transistor is connected to the first wire. A second terminal of the first transistor is connected to the gate electrode of the first transistor through the second transistor and connected to the third wire through the third transistor. A first electrode of the

display element is connected to the second terminal of the first transistor through the fourth transistor and connected to one electrode of the first capacitor through the fifth transistor

[0031] Another mode of the invention is a driving method of a display device with first to fourth periods within one frame period. The display device includes a first capacitor, a display element, first to fifth transistors, and first and second wires. In the first period, a charge is accumulated in the display element. In the second period, a charge is accumulated in the capacitor. In the third period, one electrode of the first capacitor and the first wire are electrically connected, the other electrode of the first capacitor and a first terminal of the fifth transistor are electrically connected, a second terminal of the fifth transistor and one electrode of the display element are electrically connected, the other electrode of the display element and the second wire are electrically connected, and the fifth transistor is turned on, thereby the charge accumulated in the display element and the charge accumulated in the first capacitor are divided into the display element and the first capacitor. In the fourth period, a first terminal of the first transistor and the first wire are electrically connected, a second terminal of the first transistor and a first terminal of the fourth transistor are electrically connected, the fourth transistor and one electrode of the display element are electrically connected, the other electrode of the display element and the second wire are electrically connected, and the first and fourth transistors are turned on, thereby the display element emits light.

[0032] In the invention, a potential of a first wire connected to a cathode side of a display element is the same or almost the same as a potential of a second wire connected to an anode side of the display element in first to third periods. In a forth period, a potential of the first wire connected to a cathode side of the display element is lower than a potential of the second wire connected to an anode side of the display element

[0033] In the invention, a display element also functions as a second capacitor.

[0034] In the invention, a potential of one of first and second wires changes.

[0035] In the invention, first to fifth transistors may have the same polarity.

[0036] In the invention, a first transistor is a p-channel transistor.

[0037] In the invention, a first transistor is an n-channel transistor.

[0038] As described above, a threshold holding capacitor Ct is replaced by capacitance Cel of a display element; therefore, a data current may be increased compared to a drive current of the display element without providing Ct. In addition, an aperture ratio can be increased because Ct is not provided in a pixel. When the aperture ratio is high, the capacitance Cel of the display element becomes large; therefore, a data current may be further increased. In this manner, an increase in aperture ratio leads to an increase in data current, which generates a synergistic and significant effect.

#### BRIEF DESCRIPTION OF DRAWINGS

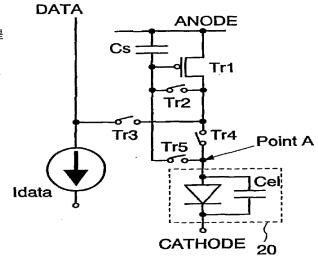

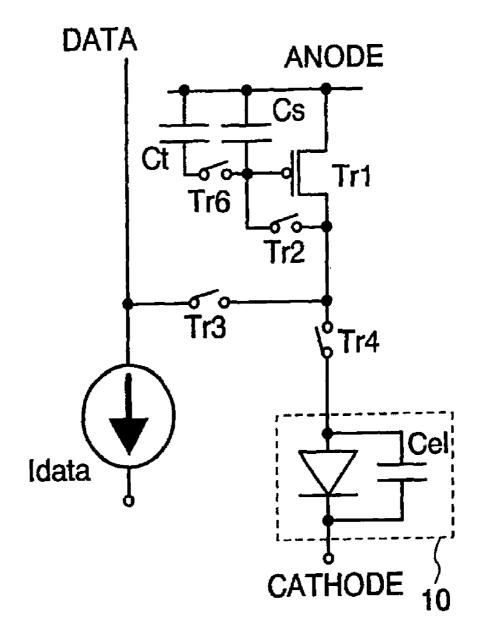

[0039] FIG. 1 is a diagram showing a pixel circuit of a display device of the invention.

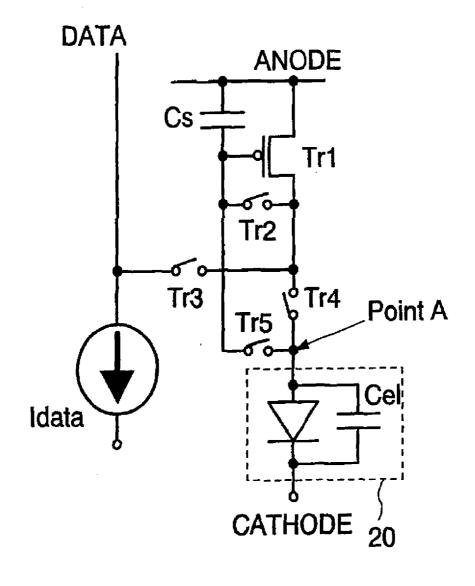

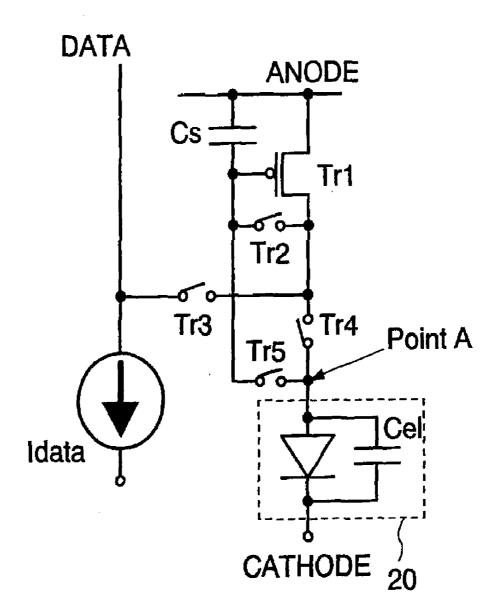

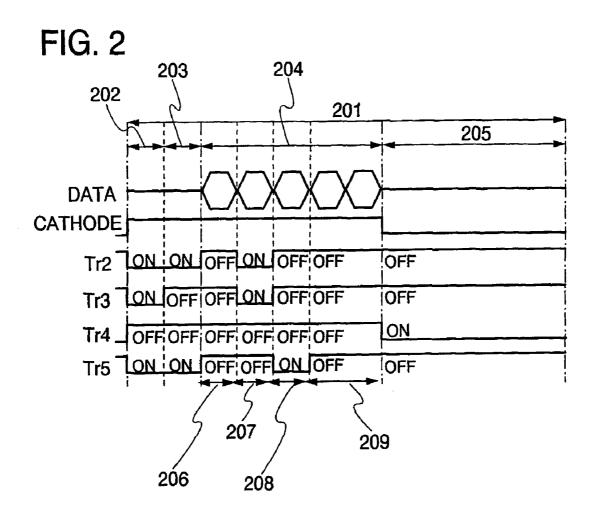

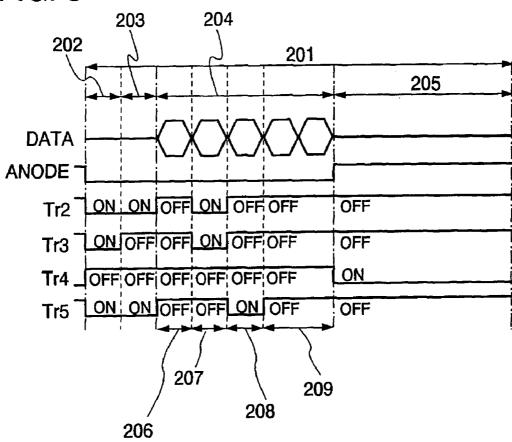

[0040] FIG. 2 is a diagram showing a driving method of a pixel circuit of a display device of the invention.

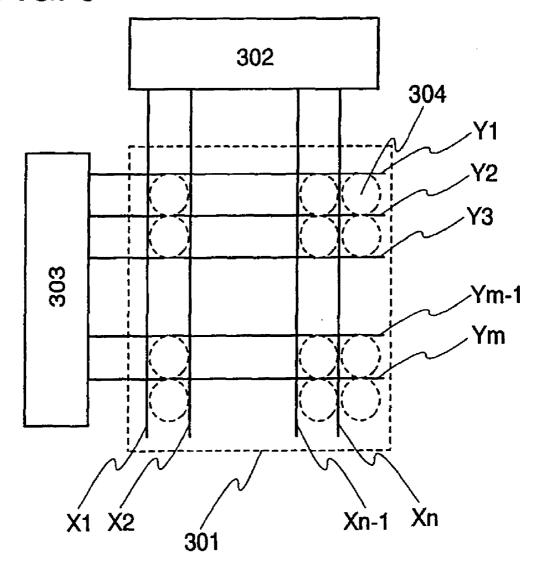

[0041] FIG. 3 is a diagram showing a structure of a display device of the invention.

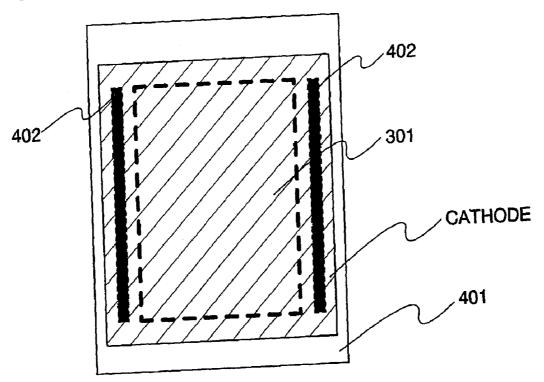

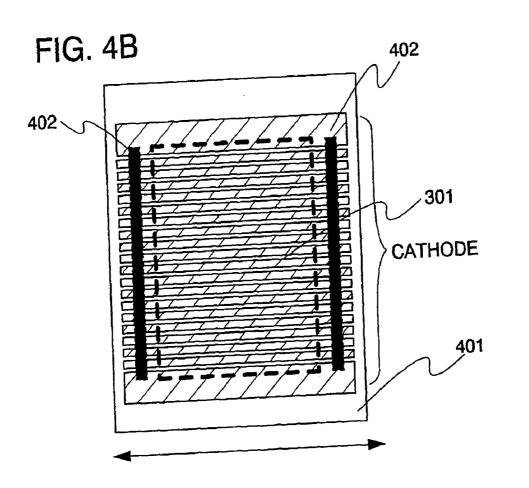

[0042] FIGS. 4A and 4B are diagrams each showing a shape of an electrode of a display device of the invention.

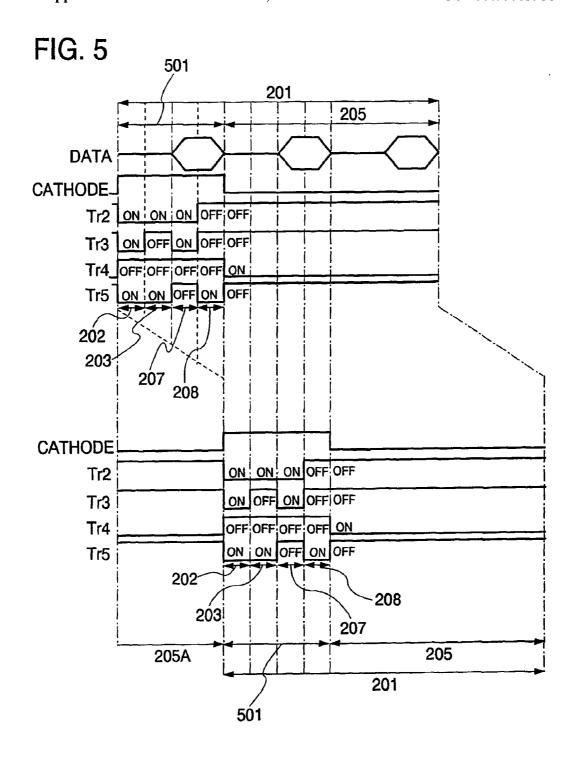

[0043] FIG. 5 is a diagram showing a driving method of a pixel circuit of a display device of the invention.

[0044] FIG. 6 is a diagram showing a driving method of a pixel circuit of a display device of the invention.

[0045] FIG. 7 is a diagram showing a pixel circuit of a display device of the invention.

[0046] FIG. 8 is a diagram showing a pixel circuit of a display device.

[0047] FIG. 9 is a diagram showing a pixel circuit of a display device.

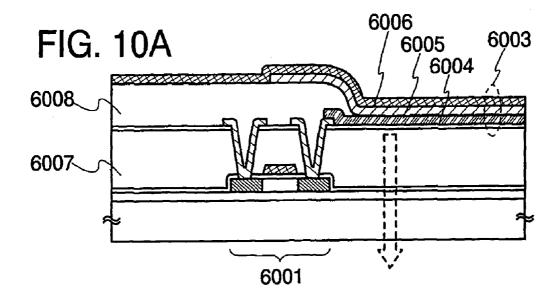

[0048] FIGS. 10A to 10C are diagrams each showing a manufacturing step of a display device of the invention.

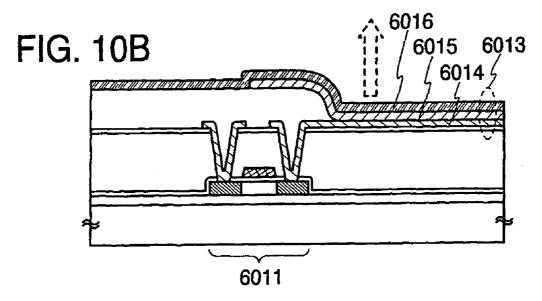

[0049] FIGS. 11A to 11F are diagrams each showing an electronic apparatus of the invention.

[0050] FIGS. 12A and 12B are diagrams each showing a pixel of the invention.

[0051] FIGS. 13A and 13B are diagrams each showing a pixel of the invention.

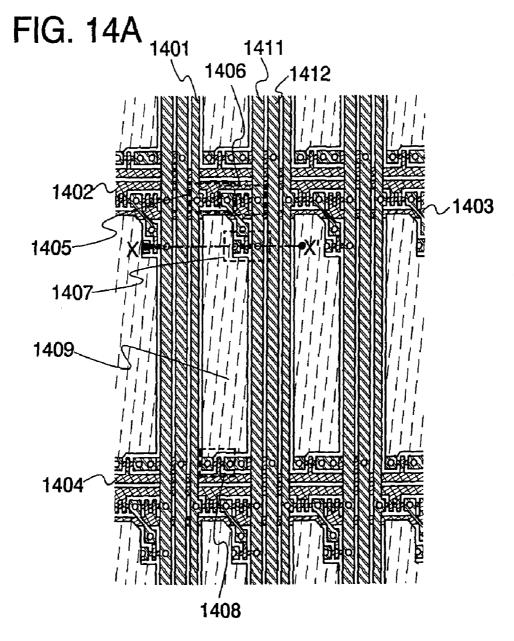

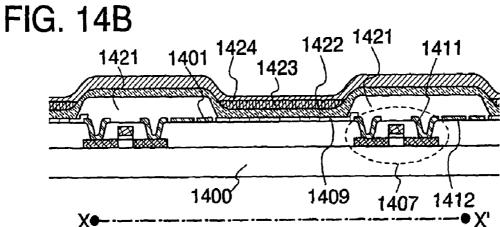

[0052] FIGS. 14A and 14B are diagrams each showing a pixel of the invention.

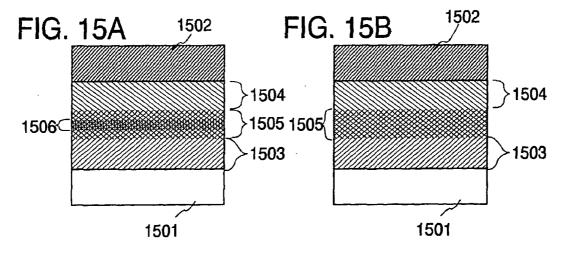

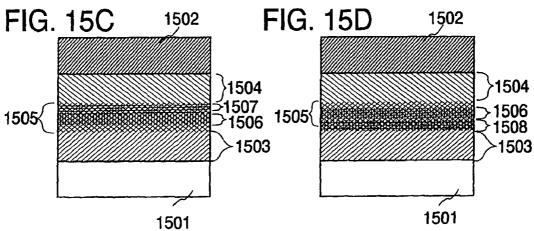

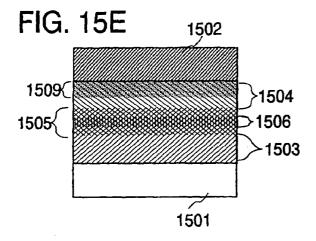

[0053] FIGS. 15A to 15E are diagrams each showing structures of an EL element of the invention.

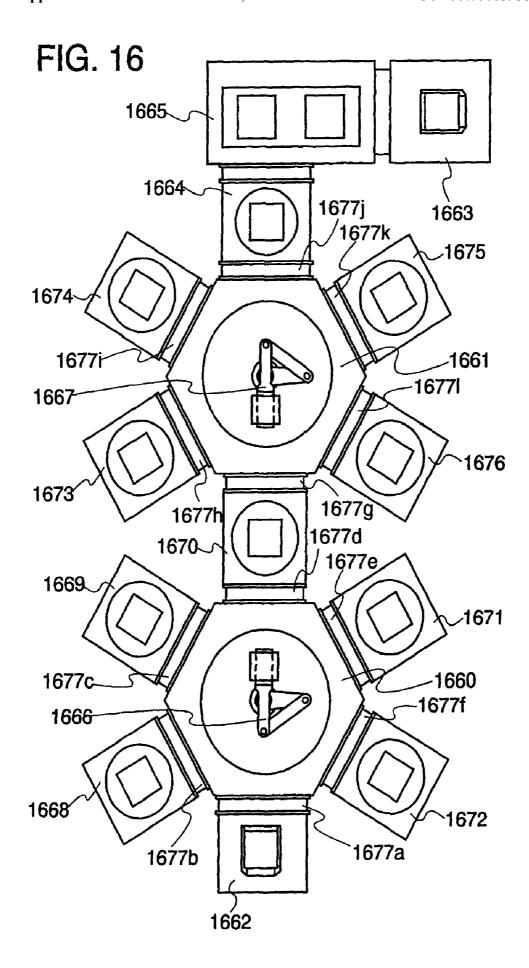

[0054] FIG. 16 is a diagram showing a vapor deposition apparatus for manufacturing a display element of the invention

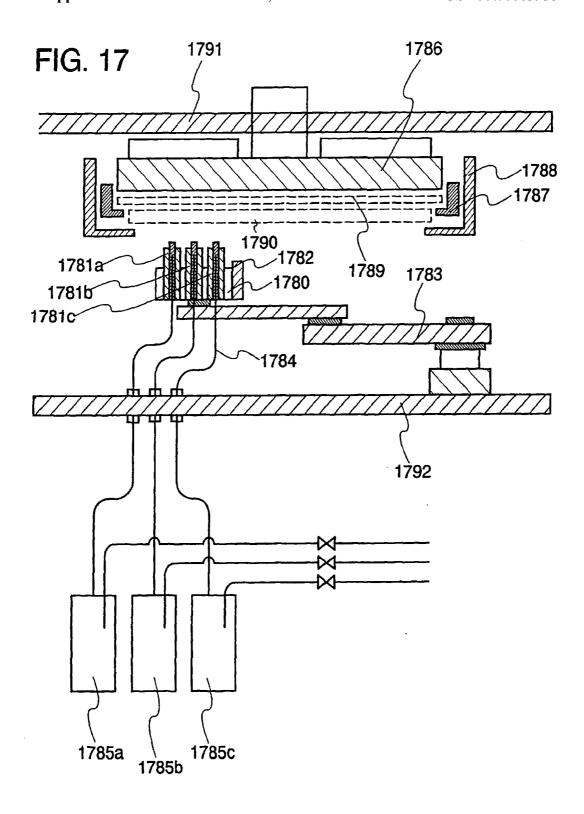

[0055] FIG. 17 is a diagram showing a deposition process chamber of a vapor deposition apparatus of the invention.

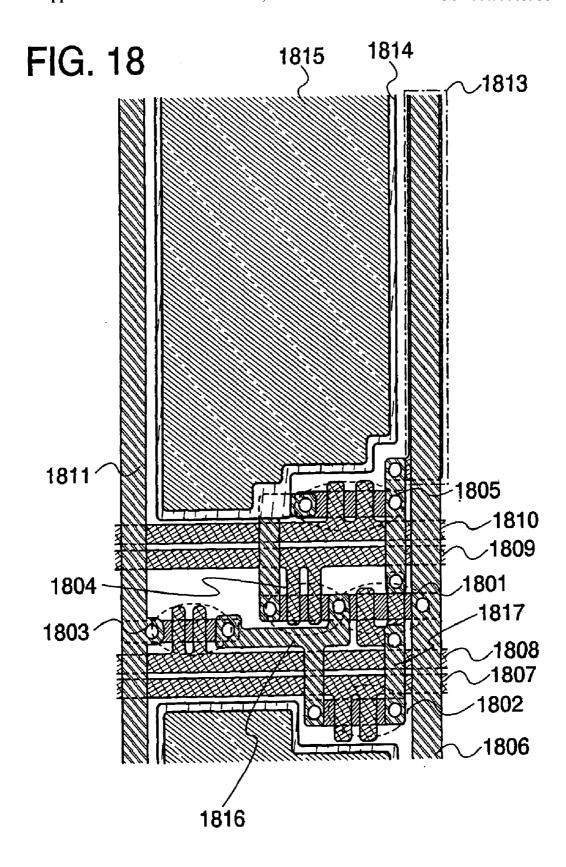

[0056] FIG. 18 is a diagram showing a pixel of the invention.

## BEST MODE FOR CARRYING OUT THE INVENTION

[0057] Although the invention will be fully described by way of embodiment modes with reference to the accompanying drawings, it is to be understood that various changes and modifications will be apparent to those skilled in the art. Therefore, unless such changes and modifications depart from the scope of the invention, they should be construed as being included therein.

[0058] Note that in the specification, a connection means being electrically connected unless specifically described. A disconnection means not being connected and being electrically separated.

#### Embodiment Mode 1

[0059] In this embodiment mode, first, description is made of a display device of the invention with reference to FIG. 3. The display element of the invention includes a data line driver circuit 302 as a peripheral driver circuit, a scan line

driver circuit 303, n data lines (X1 to Xn) (n is an integer) driven by the data line driver circuit 302, m scan lines (Y1 to Ym) (m is an integer) driven by the scan line driver circuit 303, a plurality of pixel circuits 304 arranged in a position where the m scan lines (m is more than one) and the n data lines cross, and a pixel portion 301 including the plurality of pixel circuits 304. A selection signal is transmitted by the scan lines, and a data current for showing an image signal flows through the data lines. Note that although FIG. 3 shows a case where one pixel circuit 304 is provided with one data line and one scan line, the invention is not limited to this, and one pixel circuit 304 may be provided with a plurality of scan lines and data lines. As described above, the number of pixels, to which a data current is written simultaneously, can be increased, and writing time can be reduced. In addition, the number of driver circuits is not limited in the invention, and a plurality of data line driver circuits and scan line driver circuits may be provided.

[0060] Next, description is made of a structure of the pixel circuit 304 with reference to FIG. 1. The plurality of pixel circuits 304 each include a first power supply line ANODE, a second power supply line CATHODE, a data line DATA for supplying a data current Idata, a display element which also functions as a capacitor Cel, a switch element Tr3 for selecting a pixel to which Idata is written, a first transistor (also referred to as a driving transistor) Tr1 which is connected to the display element in series and controls a current flowing to the display element, a capacitor Cs which is connected to a gate electrode of the driving transistor Tr1 and holds a voltage between a gate and a source (gate-source voltage) Vgs (data) high enough to supply a current value of Idata when Idata is supplied to the driving transistor Tr1, a switch element Tr2 which connects or disconnects between the gate electrode and a drain electrode of the driving transistor Tr1, a switch element Tr4 which is connected to the display element in series and connects or disconnects between the display element and the driving transistor Tr1, a switch element Tr5 which connects and disconnects between the capacitor Cs and the display element. A circuit diagram shows a circuit including an EL element 20 provided as a display element, a light emitting diode and a capacitor are provided; however, the EL element functions both as a light emitting element and as a capacitor. The pixel circuit of the invention can store a threshold voltage of the driving transistor Tr1 without providing a threshold holding capacitor Ct by using the capacitor Cel of the EL element. Note that in the pixel circuit 304, the display element can be driven by changing a potential of the first power supply line ANODE and a potential of the second power supply line CATHODE. In addition, the second power supply line CATHODE may be connected to all pixel circuits in com-

[0061] An element of various modes may be employed as an element which functions as a switch, such as an electrical switch and a mechanical switch. That is, as long as a flow of current can be controlled, it is not limited to a specific form of a switch, and various elements may be used. For example, a transistor, a diode (a PN diode, a PIN diode, a Schottky diode, a diode-connected transistor, or the like), or a logic circuit of a combination thereof may be employed. When a transistor is used as a switch, a thin film transistor (also referred to as TFT) may be employed. A thin film transistor may also be employed as a driving transistor. In the case where a transistor is used as a switch, polarity (conductivity

type) thereof may be either p-channel or n-channel, and all transistors may have the same polarity. Generally, a p-channel transistor has high reliability, and an n-channel transistor has a larger on current. Due to the aforementioned, either of the polarity is selected. However, a transistor with a smaller off current is preferably employed when it is preferable that an off current is smaller. As for a transistor with small off current, a transistor provided with an LDD region, a transistor with a multi-gate structure, and the like may be used. In addition, it is preferable to employ an n-channel transistor when operating in a state where a potential of a source terminal of the transistor, which operates as a switch, is close to a low potential side power source (Vss, GND, 0V, or the like), whereas it is preferable to employ a p-channel transistor when operating in a state where a potential of the source terminal of the transistor is close to a high potential side power source (Vdd or the like). This is because the transistor can be easily operated as a switch since an absolute value of a gate-source voltage thereof can be set large. Note that a CMOS switch may also be applied by using both n-channel and p-channel transistors. In the case where a CMOS switch is employed, the switch can be operated appropriately even when circumstances are changed in such a manner that a voltage inputted through the switch (in other words, a input voltage) is higher or lower than an output voltage.

[0062] However, polarity of the driving transistor Tr1, which controls a current flowing to the EL element, is decided by a potential of the first power supply line ANODE which is connected to the driving transistor Tr1 when the EL element 20 emits light. For example, in the case where an anode of the EL element 20 is connected to the driving transistor Tr1 as shown in FIG. 1, a current passes through the first power supply line ANODE, the driving transistor Tr1, and the EL element 20 in this order when the EL element 20 emits light. At this time, the first power supply line ANODE connected to the driving transistor Tr1 has the highest potential in this current path. The driving transistor Tr1 is a p-channel transistor in the case where the first power supply line ANODE has a high potential, and the driving transistor Tr1 is an n-channel transistor in the case where the first power supply line ANODE has a low potential. This is because a current value supplied to a transistor which operates in saturation region changes depending on a gatesource voltage thereof: therefore, it is easier to control a current value when a source electrode is connected to a power supply line if a current value is kept constant. Note that a source electrode, which is one of source and drain electrodes, is an electrode on a high potential side in the case of a p-channel transistor, and an electrode on a low potential side in the case of an n-channel transistor.

[0063] The polarity of the driving transistor Tr1 and each switching transistor are not necessarily the same. However, if the polarity of the transistors are all the same, it is favorable for cost reduction because the number of processes for manufacturing the transistors is reduced.

[0064] In addition, it is further favorable for cost reduction because an amorphous silicon TFT, which can be manufactured with a large area and at low cost, can be employed as the driving transistor Tr1 and each switch element. In the case of using an amorphous silicon TFT, polarity of transitions are the sum of the cost of the

sistors are preferably all n-channel type. FIG. 7 shows a pixel circuit using all n-channel transistors in the pixel circuit in FIG. 1.

[0065] Note that in this embodiment mode, description is made that the polarity of a switching transistor and a driving transistor are all p-channel type.

[0066] Next, a driving method of the pixel circuit of this embodiment mode shown in FIG. 1 is described with reference to FIG. 2. FIG. 2 is a timing chart, which shows a change of potential of the data line DATA, the second power supply line CATHODE, each gate electrode of switching transistors Tr2, Tr3, Tr4 and Tr5 with a horizontal axis representing time.

[0067] A drive of the display device of this embodiment mode includes one frame period 201 having an initialization period 202, a threshold writing period 203, an address period 204, and a light emitting period 205 with the one frame period 201 as one unit. Here, the initialization period 202 is a period in which a threshold writing operation is performed appropriately in the threshold writing period 203. The threshold writing period 203 is a period for writing a threshold voltage of the driving transistor Tr1 to the capacitor Cel of the EL element 20. The address period 204 is a period for writing a data current to all pixels. Note that by connecting the capacitor Cel of the EL element 20 to which the threshold voltage of the driving transistor Tr1 is written, to the capacitor Cs to which a voltage Vgs (data) between a gate and source of the driving transistor Tr1 (referred to as a gate-source voltage) is written corresponding to an data current Idata and dividing a charge therebetween, a data current can be written to a pixel with a large data current. The light emitting period 205 is a period in which the EL element 20 emits light in accordance with the data current written in the address period 204.

[0068] First, a potential of each signal line is described. A potential of the data line DATA may be lower than that of the first power supply line ANODE by an absolute value of the threshold voltage of the driving transistor Tr1 in the initialization period 202. If this condition is not satisfied, the driving transistor Tr1 is not turned on because the gatesource voltage thereof does not become equal to or higher than the threshold voltage in the threshold writing period 203, and the threshold voltage cannot be written because a current does not flow to the capacitor Cel of the EL element 20. Note that in the case of using an n-channel transistor as the driving transistor Tr1, the potential of the data line DATA in the initialization period 202 may be equal to or higher than that of the first power supply line ANODE by the absolute value of the threshold voltage of the driving transistor Tr1.

[0069] In the address period 204, the potential of the data line DATA is decided by a current value generated in a peripheral driver circuit in accordance with luminance data from image data and by an electrical characteristic of the driving transistor Tr1. That is, a potential of the data line DATA is different from time to time; therefore, a value is not decided in FIG. 2. In addition, a potential of the data line DATA in the light emitting period 205 is arbitrary because a state of the EL element 20 is not affected. That is, it may be only in the initialization period 202 that an electrical state of the data line DATA is decided by a potential.

[0070] In the initialization period 202, the threshold writing period 203, and the address period 204, a potential of the

second power supply line CATHODE may be high, and the same or almost the same as that of the first power supply line ANODE thereof. In the light emitting period 205, the potential of the second power supply line CATHODE is low and lower than that of the first power supply line ANODE thereof, and may be a potential which makes the driving transistor Tr1 operate in a saturation region when the switch Tr4 is turned on.

[0071] Although a potential of the first power supply line ANODE is not shown in FIG. 2, it is preferable to have a certain potential in view of reducing power consumption and noise

[0072] Concerning a potential of a signal inputted to the switching transistors Tr2, Tr3, Tr4, and Tr5, it may be a potential (a potential operating in a saturation region) at which a switch element is sufficiently turned on or off. It is preferable that an amplitude of a signal inputted to the gate electrode is smaller to such a degree that a function as a switch is not damaged in view of reducing power consumption and noise.

[0073] A pixel in FIG. 1 is operated by an input signal shown in the timing chart of FIG. 2 as described below. First, a light emitting period 205A of a former frame is shifted to the initialization period 202 of a concerned frame. At that time, a potential of the second power supply line CATHODE is raised up to a potential of the first power supply line ANODE. In addition, almost simultaneously, a switch element is changed so that a point A, the data line DATA, the gate electrode and drain electrode of the driving transistor Tr1 are electrically connected, and a potential of the data line DATA is set lower than the potential of the first power supply line ANODE by an absolute value of the threshold voltage of the driving transistor Tr1. A condition of each switch element is arbitrary in order to realize this state, and as shown by the initialization period 202 in FIG. 2, for example, the switch elements Tr2, Tr3 and Tr5 may be turned on and Tr4 may be turned off. In realizing such a state, a potential of the point A, the gate electrode and drain electrode of the driving transistor Tr1 are initialized to a value lower than the potential of the first power supply line ANODE by the absolute value of the threshold voltage of the driving transistor Tr1.

[0074] Note that the potential of the second power supply line CATHODE is lower than that of the point A (also referred to as reverse bias) in the initialization period 202; therefore, a forward current is not applied to the EL element 20, which emits no light. In addition, the EL element 20 can obtain a longer lifetime and higher reliability by applying a reverse bias voltage.

[0075] By applying the reverse bias voltage to the EL element 20, a defect and reliability of the EL element 20 can be improved. The EL element 20 sometimes causes an initial defect of a short circuit between an anode and a cathode owing to adhesion of foreign materials, a pinhole caused by a minor protrusion of the anode or the cathode, or heterogeneity of deposition of an electroluminescent material. When such an initial defect occurs, lighting and non-lighting are not performed in accordance with a signal, and most current flows to a short-circuited element. As a result, display of an image is not performed well. The defect may also happen in an arbitrary pixel.

[0076] Consequently, when the reverse bias voltage is applied to the EL element 20 as in this embodiment mode,

a local current is supplied to a short-circuited part, and the short-circuited part produces heat and can be oxidized or carbonized. Therefore, the short-circuited part can be insulated, a current is supplied to a region except the short-circuited part, and thereby the EL element 20 can be operated normally. As described above, if the initial defect occurs, it can be resolved by applying the reverse bias voltage. Note that such a short-circuited part can be insulated before shipment. For example, the switch elements Tr3 and Tr4 of all pixels are turned on, and the potential of the data line DATA is made lower than the potential of the second power supply line CATHODE; therefore, the reverse bias can be applied before shipment.

[0077] A short circuit between an anode and a cathode may occur as time passes in addition to an initial defect. Such a defect is also called a progressive defect. By applying the reverse bias voltage to the EL element 20 as in this embodiment mode, the progressive defect can be resolved if it occur, and the EL element 20 can be operated normally.

[0078] In addition, image burn-in can be prevented by applying the reverse bias voltage. The image burn-in occurs in accordance with a deterioration state of the EL element 20. The deterioration state can be decreased by applying the reverse bias voltage; therefore, the image burn-in can be prevented.

[0079] Generally, the deterioration of the EL element 20 progresses in an early stage, and a proceeding of deterioration is lessened as time passes. That is, the EL element 20 which is once deteriorated is less likely to be further deteriorated. As a result, the deterioration state of the EL element 20 varies. For resolving this, all the EL elements 20 may emit light before shipment or when an image is not displayed. At this time, deterioration can be caused even in an element which is not deteriorated, and the deterioration state of all the EL element 20 can be averaged.

[0080] Note that a timing for raising the potential of the second power supply line CATHODE and a timing for changing each switch element may be whether each switch element is switched after the potential of the second power supply line CATHODE is raised, or each switch element is switched before the potential of the second power supply line CATHODE is raised so as not to change the potential of the point A a lot. This is because time for stabilizing the potential is considered since parasitic capacitance connected to the second power supply line CATHODE is large. Note that an object of providing the initialization period 202 is to certainly carry out an threshold writing operation in the threshold writing period 203 described below, thus it is not always required to provide the initialization period 202 if the threshold writing operation is certainly carried out. However, it is preferable that the initialization period 202 is provided for certainly performing the threshold writing operation because the potential of the point A is changed as the potential of the second power supply line CATHODE is raised. In this embodiment mode, although description is made of the case where the data line DATA is employed for initialization, another wire such as an exclusive power supply line or a scan line may be employed for initialization instead of the data line DATA.

[0081] Next, after the potential of the point A is set lower than the potential of the first power supply line ANODE by the absolute value of the threshold voltage of the driving

transistor Tr1, a period is shifted to a period (corresponding to the threshold writing period 203) for changing a voltage, which is supplied to both ends of electrodes of the capacitor Cel, into the threshold voltage of the driving transistor Tr1. At this time, a switch element is switched so that the point A, the gate electrode and the drain electrode of the driving transistor Tr1 are electrically connected and become a floating state. A condition of each switch element for realizing this state is arbitrary. For example, the switch elements Tr2 and Tr5 are turned on, and the switch elements Tr3 and Tr4 are turned off as shown in the threshold writing period 203 of FIG. 2. By realizing such a state, a current flows to the capacitor Cs from the first power supply line ANODE through the driving transistor Tr1. The driving transistor Tr1 is turned off and a current stops flowing when the gatesource voltage of the driving transistor Tr1 becomes the threshold voltage thereof.

[0082] At this time, the point A, the gate electrode and drain electrode of the driving transistor Tr1 are electrically connected; therefore, the potential of the point A is lower than the potential of the first power supply line ANODE by the absolute value of the threshold voltage of the driving transistor Tr1. The voltage applying to the both electrodes of the capacitor Cs at this time becomes the threshold voltage of the driving transistor Tr1. On the other hand, the potential of the point A is lower than the potential of the first power supply line ANODE by the absolute value of the threshold voltage of the driving transistor Tr1 regardless of the potential of the second power supply line CATHODE; therefore, the voltage applying to the both electrodes of the capacitor Cel becomes the threshold voltage of the driving transistor Tr1 in the case where the potential of the second power supply line CATHODE is the same or almost the same as the potential of the first power supply line ANODE. In addition, it is preferable not to change the potential of the second power supply line CATHODE from that in the initialization period 202 because the potential of the point A also changes as the potential of the second power supply line CATHODE changes.

[0083] Next, a period is shifted to the address period 204 including a period for writing a data current by each scan line. In the address period 204, a period before selecting the pixel is called a pre-writing period 206, a period for writing a data current to the pixel is called a data writing period 207, a period for rewriting a voltage applied to the capacitor Cs of the pixel by a voltage held in the capacitance Cel is called a Cs rewriting period 208, and a period after the Cs rewriting period 208 is over is called a post-rewriting period 209. In the pixel circuit of the invention, the capacitance Cel of the EL element 20 is applied without providing the threshold holding capacitor Ct, and the Cs rewriting period 208 is provided for rewriting the voltage applied to the capacitor Cs of the pixel by the voltage holding to the capacitance Cel. Note that as a data current is written to each pixel connected to each scan line (Y1 to Ym), a timing and length of each period in the address period 204 shown in FIG. 2 are one example. A timing for the data writing period 207, and a length of the pre-writing period 206 and a length of the post-rewriting period 209 are different depending on each pixel connected to each scan line (Y1 to Ym). Note that in the address period 204, as the potential of the second power supply line CATHODE, the potential of the point A is also changed; therefore, an accurate gate-source voltage of the driving transistor Tr1 cannot be obtained in the Cs rewriting

period 208, and it is preferable that the potential of the second power supply line CATHODE is not changed from that in the initialization period 202 and the threshold writing period 203.

[0084] In the pre-writing period 206, the point A sets to be a floating state so that the threshold voltage of the driving transistor Tr1 obtained in the aforementioned threshold writing period 203 is held in the capacitor Cel. Each element except for a switch element in the pixel (in particular, the capacitor Cs, the driving transistor Tr1, and the EL element 20) and the data line DATA are set not to be electrically connected so as not to prevent writing to a pixel connected to a selected scan line other than a scan line connected to the concerned pixel. A condition of each switch element for realizing such a state is arbitrary, and for example, the switch elements Tr2, Tr3, Tr4 and Tr5 are turned off as shown in the pre-writing period 206 of FIG. 2.

[0085] In the data writing period 207, the point A sets to be a floating state so that the capacitor Cel holds the threshold voltage of the driving transistor Tr1 obtained in the aforementioned threshold writing period 203. The data line DATA and the gate and the drain electrodes of the driving transistor Tr1 are electrically connected to each other, which are prevented from being electrically connected to the other elements except for a switch element. A condition of each switch element for realizing such a state is arbitrary, and for example, the switch elements Tr2 and Tr3 are turned on, and the switch elements Tr4 and Tr5 are turned off as shown in the threshold writing period 203 of FIG. 2. By realizing such a state, the data current Idata flows to the driving transistor Tr1, and the gate-source voltage (Vgs (data)), which is high enough for the driving transistor Tr1 to supply the data current Idata, is supplied to the capacitor Cs.

[0086] In the Cs rewriting period 208, the capacitor Cel which holds the threshold voltage of the driving transistor Tr1 obtained in the aforementioned threshold writing period 203 is electrically connected to the capacitor Cs which holds the gate-source voltage high enough for the driving transistor Tr1 to supply the data current Idata, and the point A is prevented from being electrically connected to the other elements except for a switch element (except for the gate electrode of the driving transistor Tr1). A condition of each switch element for realizing such a state is that, for example, the switch elements Tr2, Tr3 and Tr4 are turned off, and the switch element Tr5 is turned on as shown in the Cs rewriting period 208 of FIG. 2. By realizing such a state, the gatesource voltage (also referred to as Vgs (oled)), which is high enough to supply a current Ioled satisfying Formula 2, is supplied to the capacitor Cs. The current Ioled is described by the following formula.

$$Ioled = \left(\frac{Cs}{(Cel + Cs)}\right)^2 \times Idata$$

[Formula 2]

[0087] In the post-rewriting period 209, the gate electrode of the driving transistor Tr1 is set to be a floating state so that the voltage Vgs (oled) applied to the capacitor Cs in the Cs rewriting period 208 can be held, and each element except for a switch element in the pixel (in particular, the capacitor Cs, the driving transistor Tr1, and the EL element 20) and the data line DATA are set not to be electrically connected so as

not to prevent writing to a pixel connected to a selected scan line other than a scan line connected to the pixel. A condition of each switch element for realizing such a state is arbitrary, and for example, the switch elements Tr2, Tr3, Tr4 and Tr5 are turned off as shown in the post-rewriting period 209 of FIG. 2.

[0088] As described above, in the address period 204, a gate-source voltage, which is high enough to supply a current Ioled corresponding to each luminance, is written to the capacitor Cs in all pixels by writing data sequentially to each scan line (Y1 to Ym). Then, the voltage is shifted in the next one frame period 201 and held in the capacitor Cs. Note that description of the number to divide the address period 204 in FIG. 2 is one example, and this embodiment mode is not limited to this. For example, the number to divide the address period 204 is the same or the almost same as the number of the scan lines. In addition, a plurality of scan lines may be driven using a plurality of the data line driver circuits 302 in order to shorten the address period 204. In the case where two scan lines are driven by using two data line driver circuits 302, for example, the number to divide the address period 204 is half the number of the scan lines

[0089] Next, a period is shifted to the light emitting period 205, in which the EL element 20 emits light in accordance with the gate-source voltage Vgs (oled) of the driving transistor Tr1 held in the aforementioned address period 204. At this time, the driving transistor Tr1 and the EL element 20 are connected in series, and the gate-source voltage Vgs (oled) of the driving transistor Tr1 holding in the aforementioned address period 204 is held; therefore, the gate electrode of the driving transistor Tr1 is set to be a floating state, and an element except for each switch element in each pixel and the data line DATA are set not to be electrically connected. A condition of each switch element is that, for example, the switch element Tr4 is turned on, and the switch elements Tr2, Tr3, and Tr5 are turned off as shown in the light emitting period 205 of FIG. 2. By realizing such a state, the current Ioled satisfying Formula 2 flows to the driving transistor Tr1 and the EL element 20, and the EL element 20 emits light at luminance in accordance with the data current Idata.

[0090] As the pixel circuit and the driving method thereof in this embodiment mode, the threshold holding capacitor Ct is replaced by the capacitance Cel of an EL element. As a result, a data current can be increased in response to a drive current of the EL element without providing Ct. This may be also understood from a comparison of the pixel circuit and the driving method thereof in this embodiment mode with a conventional pixel circuit shown in FIG. 9 and Formula 1, which expresses a current flowing to the EL element 20.

[0091] In this embodiment mode, an aperture ratio can be increased because Ct is not provided in a pixel. The increase in aperture ratio leads to an increase in the capacitance Cel of an EL element; therefore, a data current can be further increased. In this manner, the increase in aperture ratio leads to the increase in data current, which generates a synergistic and significant effect.

#### Embodiment Mode 2

[0092] Next, description is made of a second mode of a display device of the invention with reference to FIGS. 4A, 4B, and 5.

[0093] A pixel circuit in this embodiment mode may be applied to FIG. 1 explained in Embodiment Mode 1. Note that in this embodiment mode a manufacturing method of the second power supply line CATHODE is different from the mode explained in Embodiment Mode 1, which can generate a particular effect. Description is made of a mode of the second power supply line CATHODE with reference to FIGS. 4A and 4B.

[0094] FIG. 4A is a schematic view of the second power supply line CATHODE in the display device explained in the aforementioned Embodiment Mode 1. The second power supply line CATHODE in FIG. 4A has a mode of being connected to all pixel circuits in common as already described in Embodiment Mode 1. A pixel portion 301 is formed over a substrate 401, over which an EL element is formed as a display element, over which a contact region 402 with a lower electrode is formed, over which the second power supply line CATHODE is formed over a whole area by vapor deposition, which can be directly applied to a common electrode.

[0095] Note that in the case of using an EL element as a display element, the second power supply line CATHODE may be processed in shape by photolithography; however, it is considered that a damage to an EL element by the process is large. In the case where the second power supply line CATHODE is formed by vapor deposition using a vapordeposition mask, the second power supply line CATHODE can be processed in shape without giving great damage to the EL element. In this embodiment mode, description is made of the case where the second power supply line CATHODE is processed in shape in parallel to scan lines (Y1 to Ym) represented by an arrow shown in FIG. 4B. Note that it is preferable that the number of dividing the second power supply line CATHODE by processing shape is the same as the number of scan lines, which is one line per one pixel row which is in parallel with the scan line. However, the number of partitions itself is arbitrary, and the number of the second power supply line CATHODE to be processed may be freely decided.

[0096] As the region 402 in contact with the second power supply line, it is preferable that the second power supply line CATHODE is controlled individually in a circuit connected to the second power supply line CATHODE or to the lower electrode.

[0097] Description is made of a driving method with reference to FIG. 5, which is an operation of the pixel circuit 304 in this embodiment mode and can be realized by making the second power supply line CATHODE peculiar to each scan line. FIG. 5 shows a timing chart of a concerned line and a timing chart of a next line. A line means a pixel group connected to the same scan line.

[0098] In this embodiment mode, a structure of the pixel circuit 304 can employ to that of FIG. 1 as in Embodiment Mode 1.

[0099] FIG. 5 is a timing chart, which shows a change of potential of the data line DATA, the second power supply line CATHODE, each gate electrode of the switching transistors Tr2, Tr3, Tr4 and Tr5 with a horizontal axis representing time. In a drive of the display device of this embodiment mode, one frame 201 includes a one scan line writing period 501 and a light emitting period 205 as one

unit. The one scan line writing period 501 includes a initialization period 202, a threshold writing period 203, a data writing period 207, a Cs rewriting period 208.

[0100] When the concerned line finishes light emission in a former frame and shifts to the one scan line writing period 501, the line is rewritten from Vgs of a former line to a Vgs (oled) of a concerned line, which corresponds to a data current through a state of the initialization period 202, the threshold writing period 203, the data writing period 207 and the Cs rewriting period 208, and may be shifted to a light emitting state again.

[0101] Here, description of each state in detail is omitted as is already described in Embodiment Mode 1. However, an input signal to the data line DATA is different from that of Embodiment Mode 1 and is required to be a lower value than the first power supply line ANODE by the absolute value of the threshold voltage of the driving transistor Tr1 so as to be initialized individually by each line before writing data to each line. Note that in FIG. 5 the initialization period 202 is just before the threshold writing period 203, however it is not required to be just before the threshold writing period 203 particularly, and initialization may be performed before the threshold writing period 203. For example, the concerned line can be initialized when the data line DATA has a lower value than the first power supply line ANODE by the absolute value of the threshold voltage of the driving transistor Tr1 in two lines before the concerned lines. After initialization, Tr3 is turned off, and the threshold voltage is written to the capacitor Cel of an EL element. Then data writing or the like are performed in a selecting period. In performing as described above, the threshold writing period 203 can be set long enough.

[0102] Note that although a length of a horizontal axis shown in FIG. 5 is almost equally spaced, this embodiment mode is not limited to this, and a length of each period may be decided appropriately as needed.

[0103] A driving method of this embodiment mode shown in FIG. 5 is characterized by forming the second power supply line CATHODE in parallel with the scan lines. In the case where the second power supply line CATHODE of the concerned line is changed in order to be written to the concerned line, an operation of the lines other than the concerned line is not effected. Therefore, the other lines may continue to emit light with Vgs (oled) being held in accordance with the data current of a former line, while the concerned line is selected and the data current is written thereto. That is, a ratio (duty ratio) of light emitting period within the one frame period 201 is substantially improved. When the duty ratio is high, even momentary luminance of a light emitting element is smaller than that with smaller duty ratio, it is recognized as the same luminance. Therefore, in addition to the effects in Embodiment Mode 1, a driving voltage can be smaller, power consumption can be reduced, and reliability can be improved.

#### Embodiment Mode 3

[0104] Next, description is made of a third mode of a display device of the invention with reference to FIG. 6. In this embodiment mode, a driving method of the display device by alternating a first power supply line ANODE is described. In this embodiment mode, a second power supply line CATHODE may be connected to all pixels in common,

10

which is described in this embodiment mode. However, the second power supply line CATHODE may be processed in shape in this embodiment mode.

[0105] In FIG. 6, an input signal is described in the case where the display device of the invention is driven by alternating the first power supply line ANODE with polarity of all transistors being p-channel. One frame includes the initialization period 202, the threshold writing period 203, the address period 204, the light emitting period 205, which is the same as the drive shown in Embodiment Mode 1, and a performance of circuits in each period is almost the same as well. Therefore, in this embodiment mode, description is mainly made of different points from Embodiment Mode 1.

[0106] First, a potential of each signal line is described. In the initialization period 202, the threshold writing period 203, and the address period 204, a potential of the first power supply line ANODE may be low and be the same or almost the same as a potential of the second power supply line CATHODE. In the light emitting period 205, a potential of the first power supply line ANODE may be high and higher than a potential of the second power supply line CATHODE at that time, and may be a potential at which the driving transistor Tr1 operates in a saturation region when the switch element Tr4 is turned on.

[0107] A potential of the second power supply line CATH-ODE is not shown in FIG. 6; however, it is preferable to be a constant potential in view of reducing power consumption and noise.

[0108] A potential of a data line DATA in the initialization period 202 may be lower than a potential of the first power supply line ANODE by an absolute value of a threshold voltage of the driving transistor Tr1. If this condition is not satisfied, the driving transistor Tr1 is not turned on because a gate-source voltage thereof is not more than the threshold voltage in the threshold writing period 203, and the threshold voltage cannot be written to the EL element 20 because a current does not flow to the capacitor Cel of the EL element 20. Note that in the case of using an n-channel transistor as the driving transistor Tr1, the potential of the data line DATA in the initialization period 202 may be equal to or higher than that of the first power supply line ANODE by the absolute value of the threshold transistor of the driving transistor Tr1.

[0109] A potential of the data line DATA in the address period 204 is decided by a value of a data current generated in a peripheral driver circuit in accordance with luminance data from image data and by an electrical characteristic of the driving transistor Tr1. That is, a potential of the data line DATA is different from time to time, so that a value is not decided in FIG. 6. In addition, a potential of the data line DATA in the light emitting period 205 is arbitrary because a state of the EL element 20 is not affected. That is, it may be only in the initialization period 202 that an electrical state of the data line DATA is decided by a potential.

[0110] A potential of a signal inputted to the switching transistors Tr2, Tr3, Tr4 and Tr5 may be a potential (potential operating in a linear region) at which the switch element is sufficiently turned on or off. An amplitude of a signal inputted to a gate electrode is preferably smaller to such a degree that a function as a switch is not damaged in view of reducing power consumption and noise.

[0111] In this embodiment mode, a different part of an operation from that in Embodiment Mode 1 is that the potential of the second power supply line CATHODE is not changed and the potential of the first power supply line ANODE is changed so as to be equal to the potential of the second power supply line CATHODE. There are the following three differences in specific. First, when the light emitting period 205 is shifted to the initialization period 202, the potential of the first power supply line ANODE is lowered. Second, when the address period 204 is shifted to the light emitting period 205, the potential of the first power supply line ANODE is raised. And third, in the initialization period 202, the threshold writing period 203, and the address period 204, the potential of the first power supply line ANODE is set to be the same or almost the same as the potential of the second power supply line CATHODE, of which potential is low. However, the third difference described above does not affect to a circuit operation; therefore, the circuit operations in this embodiment mode and Embodiment Mode 1 are not different. Therefore, description of the circuit operation is omitted since it is the same as that in Embodiment Mode 1.

[0112] Description is made of the operation on a first point at which the potential of the first power supply line ANODE is lowered when a light emitting period 205A of a former frame is shifted to the initialization period 202 of the concerned frame. When the light emitting period 205A of the former frame is shifted to the initialization period 202 of the concerned frame, the switch elements Tr2, Tr3 and Tr5 which are off are turned on, and Tr4 which is on is turned off. And almost simultaneously, the potential of the first power supply line ANODE is lowered so as to be almost equal to the potential of the second power supply line CATHODE, and the potential of the data line DATA is lowered than the lower potential (Low state) of the first power supply line ANODE by the absolute value of the threshold voltage of the driving transistor Tr1. In Embodiment Mode 1, the potential of the data line DATA in initialization is lowered than the high potential (High state) of the second power supply line CATHODE by the absolute value of the threshold voltage of the driving transistor Tr1, which is different from this embodiment mode. Note that in the case where the driving transistor Tr1 is an n-channel transistor, the potential of the data line DATA is raised than the lower potential of the first power supply line ANODE by the absolute value of the threshold voltage of the driving transistor Tr1 in this embodiment mode. In Embodiment Mode 1, in the case where the driving transistor Tr1 is an n-channel transistor, the potential of the data line DATA is raised than the higher potential of the second power supply line CATHODE by the absolute value of the threshold voltage of the driving transistor Tr1, which is different from this embodiment mode.

[0113] Description is made of the operation on a second point at which the potential of the first power supply line ANODE is raised when the address period 204 is shifted to the light emitting period 205. When the address period 204 is shifted to the light emitting period 205, the switch elements Tr2 and Tr3 remain to be off, Tr4 which is on is turned off, and Tr5 remains to be off or is turned off. After the switch element Tr5 is accurately turned off so that one electrode of the capacitor Cs is in a floating state, the potential of the first power supply line ANODE is raised to be a higher potential. If the switch element Tr5 is not accurately turned off and one electrode of the capacitor Cs is not in a floating state, a voltage cannot be held in the

capacitor Cs when the potential of the first power supply line ANODE is raised, which is the same as Embodiment Mode 1

[0114] In this embodiment mode, advantages are described below in the case where the display device of the invention is driven by alternating a potential of the first power supply line ANODE. First, power consumption in driving can be reduced because the second power supply line CATHODE connected to large capacitance is not changed. In addition, it is easy to process to drive each scan line independently because the first power supply line ANODE can be formed on a substrate side. That is, a drive with a high duty ratio can be realized without adding a step such as mask deposition in manufacturing.

#### Embodiment Mode 4

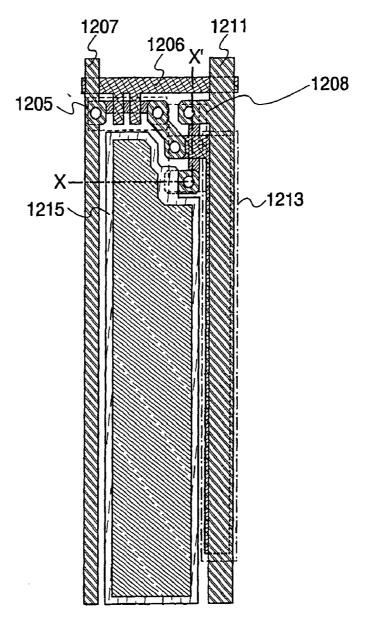

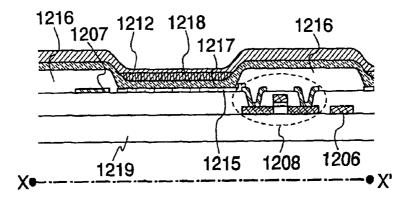

[0115] FIG. 12A shows a layout example of an element in a pixel including two TFTs per one pixel. FIG. 12B shows a cross sectional view taken along a line X-X' shown in FIG. 12A

[0116] A pixel of the invention as shown in FIG. 12A may include a first TFT 1205, a first wire 1206, a second wire 1207, a second TFT 1208, a third wire 1211, an opposite electrode 1212, a capacitor 1213, a pixel electrode 1215, a partition wall 1216, an organic conductive film 1217, an organic thin film 1218, and a substrate 1219. Note that it is preferable that the first TFT 1205 functions as a switching TFT, the first wire 1206 functions as a gate signal line, the second wire 1207 functions as a driving TFT, and the third wire 1211 functions as a power supply line.

[0117] As shown in FIG. 12A, it is preferable that a gate electrode of the first TFT 1205 is electrically connected to the first wire 1206, one of source and drain electrodes of the first TFT 1205 is electrically connected to the second wire 1207, and the other of the source and drain electrodes thereof is electrically connected to a gate electrode of the second TFT 1208 and one electrode of the capacitor 1213. Note that the gate electrode of the first TFT 1205 may include a plurality of gate electrodes as shown in FIG. 12A. As a result, a leakage current in an off state of the first TFT 1205 can be reduced.

[0118] In addition, it is preferable that one of source and drain electrodes of the second TFT 1208 is electrically connected to the third wire 1211, and the other of the source and drain electrodes of the second TFT 1208 is electrically connected to the pixel electrode 1215. As a result, a current flowing to the pixel electrode 1215 can be controlled by the second TFT 1208.

[0119] The organic conductive film 1217 may be formed over the pixel electrode 1215, over which the organic thin film (organic compound layer) 1218 may be formed. The opposite electrode 1212 may be formed over the organic thin film (organic compound layer) 1218. Note that the opposite electrode 1212 may be formed so as to be connected to all pixels in common and may be patterned using a shadow mask or the like.

[0120] Light from the organic thin film (organic compound layer) 1218 is transmitted through one of the pixel electrode 1215 and the opposite electrode 1212 to be emitted. At this time, in FIG. 12B, in the case where light is

emitted to the pixel electrode side, namely a side where a TFT and the like are formed, the pixel electrode **1215** is preferably formed of a light transmissive conductive film. In the case where light is emitted to the opposite electrode side, the opposite electrode **1212** is preferably formed of a light transmissive conductive film.

[0121] In addition, as a light emitting device for color display, an EL element which has each light emission color of R, G or B may be separately deposited, or light emission of RGB may be obtained through a color filter.

[0122] Note that the structures shown in FIGS. 12A and 12B are only examples, and a pixel layout, a cross sectional structure, a stacking order of electrodes of an EL element, and the like may have various structures other than those shown in FIGS. 12A and 12B. As for a light emitting layer, various elements such as a crystalline element, for example an LED, or an element including an inorganic thin film may be employed other than an element including an organic thin film shown in the drawings.

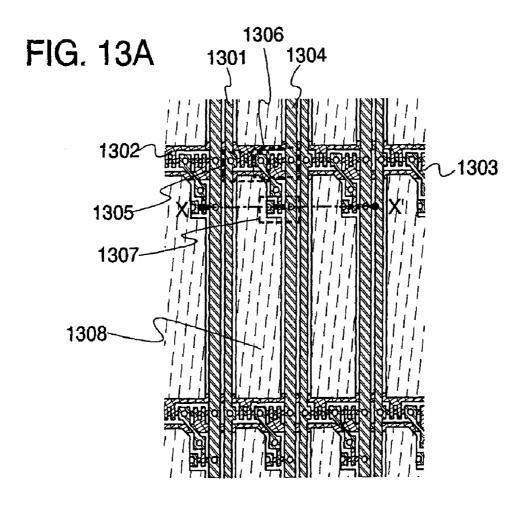

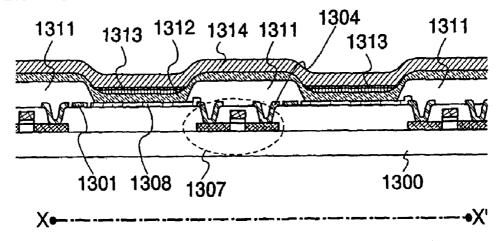

[0123] Next, description is made of a layout example of an element in a pixel including three TFTs with reference to FIG. 13A. FIG. 13B shows a cross sectional view taken along a line X-X' shown in FIG. 13A.

[0124] As shown in FIG. 13A, a pixel of the invention may include a substrate 1300, a first wire 1301, a second wire 1302, a third wire 1303, a fourth wire 1304, a first TFT 1305, a second TFT 1306, a third TFT 1307, a pixel electrode 1308, a partition wall 1311, an organic conductive film 1312, an organic thin film 1313, and an opposite electrode 1314. Note that it is preferable that the first wire 1301 functions as a source signal line, the second wire 1302 functions as a writing gate signal line, the third wire 1303 functions as an erasing gate signal line, the fourth wire 1304 functions as a power supply line, the first TFT 1305 functions as a reasing TFT, the second TFT 1306 functions as an erasing TFT, and the third TFT 1307 functions as a driving TFT.

[0125] As shown in FIG. 13A, it is preferable that a gate electrode of the first TFT 1305 is electrically connected to the second wire 1302, one of source and drain electrodes of the first TFT 1305 is electrically connected to the first wire 1301, and the other of the source and drain electrodes thereof is electrically connected to a gate electrode of the third TFT 1307. Note that the gate electrode of the first TFT 1305 may include a plurality of gate electrodes as shown in FIG. 13A, which can reduce a leakage current in an off state of the first TFT 1305.

[0126] In addition, it is preferable that a gate electrode of the second TFT 1306 is electrically connected to the third wire 1303, one of source and drain electrodes of the second TFT 1306 is electrically connected to the fourth wire 1304, and the other of the source and drain electrodes thereof is electrically connected to a gate electrode of the third TFT 1307. Note that the gate electrode of the second TFT 1306 may include a plurality of gate electrodes as shown in FIG. 13A, which can reduce a leakage current in an off state of the second TFT 1306.

[0127] In addition, it is preferable that one of source and drain electrodes of the third TFT 1307 is electrically connected to the fourth wire 1304 and the other of the source and drain electrodes thereof is electrically connected to the

pixel electrode 1308, which can control a current flowing to the pixel electrode 1308 by the third TFT 1307.

[0128] The organic conductive film 1312 may be formed over the pixel electrode 1308, over which the organic thin film (organic compound layer) 1313 may be formed. The opposite electrode 1314 may be formed over the organic thin film (organic compound layer) 1313. Note that the opposite electrode 1314 may be formed so as to be connected to all pixels in common, and may be patterned using a shadow mask or the like.

[0129] Light from the organic thin film (organic compound layer) 1313 is transmitted through one of the pixel electrode 1308 and the opposite electrode 1314 to be emitted. At this time, in FIG. 13B, in the case where a light is emitted to the pixel electrode side, namely a side of which a TFT and the like are formed, the pixel electrode 1308 is preferably formed of a light transmissive conductive film. In the case where light is emitted to the opposite electrode side, the opposite electrode 1314 is preferably formed of a light transmissive conductive film.

[0130] In addition, as a light emitting apparatus for color display, an EL element which has each light emission color of R, G or B may be separately deposited, or light emission of RGB may be obtained through a color filter.

[0131] Note that the structures shown in FIGS. 13A and 13B are examples, and a pixel layout, a cross sectional structure, a stacking order of electrodes of an EL element, and the like may have various structures other than shown in FIGS. 13A and 13B. As for a light emitting layer, various elements such as a crystalline element, for example an LED, an element including an inorganic thin film may be employed other than an element including an organic thin film shown in the drawings.

[0132] Next, description is made of a layout example of an element in a pixel including four TFTs per one pixel with reference to FIG. 14A. FIG. 14B shows a cross sectional view taken along a line X-X' shown in FIG. 14A.